|

modm API documentation

|

|

modm API documentation

|

#include <modm/platform/dma/dma.hpp>

Classes | |

| struct | RequestMapping |

Public Typedefs | |

| using | IrqHandler = void (*)(void) |

Public Types | |

| enum | Channel { Stream0 = 0, Stream1, Stream2, Stream3, Stream4, Stream5, Stream6, Stream7, Channel0 = Stream0, Channel1 = Stream1, Channel2 = Stream2, Channel3 = Stream3, Channel4 = Stream4, Channel5 = Stream5, Channel6 = Stream6, Channel7 = Stream7 } |

| enum | CircularMode : uint32_t { Disabled = 0, CircularMode::Enabled = DMA_SxCR_CIRC } |

| enum | DataTransferDirection : uint32_t { DataTransferDirection::PeripheralToMemory = 0, DataTransferDirection::MemoryToPeripheral = DMA_SxCR_DIR_0, DataTransferDirection::MemoryToMemory = DMA_SxCR_DIR_1 } |

| enum | InterruptEnable : uint32_t { DirectModeError = DMA_SxCR_DMEIE, TransferError = DMA_SxCR_TEIE, HalfTransfer = DMA_SxCR_HTIE, TransferComplete = DMA_SxCR_TCIE } |

| enum | InterruptFlags : uint8_t { FifoError = 0b00'0001, DirectModeError = 0b00'0100, Error = 0b00'1000, HalfTransferComplete = 0b01'0000, TransferComplete = 0b10'0000, All = 0b11'1101, Global = All } |

| enum | MemoryDataSize : uint32_t { Byte = 0, Bit8 = Byte, HalfWord = DMA_SxCR_MSIZE_0, Bit16 = HalfWord, Word = DMA_SxCR_MSIZE_1, Bit32 = Word } |

| enum | MemoryIncrementMode : uint32_t { Fixed = 0, MemoryIncrementMode::Increment = DMA_SxCR_MINC } |

| enum | PeripheralDataSize : uint32_t { Byte = 0, Bit8 = Byte, HalfWord = DMA_SxCR_PSIZE_0, Bit16 = HalfWord, Word = DMA_SxCR_PSIZE_1, Bit32 = Word } |

| enum | PeripheralIncrementMode : uint32_t { Fixed = 0, PeripheralIncrementMode::Increment = DMA_SxCR_PINC } |

| enum | Priority : uint32_t { Low = 0, Medium = DMA_SxCR_PL_0, High = DMA_SxCR_PL_1, VeryHigh = DMA_SxCR_PL_1 | DMA_SxCR_PL_0 } |

| enum | Request : uint32_t { Channel0 = (0 << DMA_SxCR_CHSEL_Pos), Channel1 = (1 << DMA_SxCR_CHSEL_Pos), Channel2 = (2 << DMA_SxCR_CHSEL_Pos), Channel3 = (3 << DMA_SxCR_CHSEL_Pos), Channel4 = (4 << DMA_SxCR_CHSEL_Pos), Channel5 = (5 << DMA_SxCR_CHSEL_Pos), Channel6 = (6 << DMA_SxCR_CHSEL_Pos), Channel7 = (7 << DMA_SxCR_CHSEL_Pos) } |

| enum | Signal : uint8_t { NoSignal, Ch1, Ch2, Ch3, Ch4, Com, Dac1, Dac2, Ext_rx, Ext_tx, Rx, Trig, Tx, Up } |

Public Member Functions | |

| MODM_FLAGS32 (InterruptEnable) | |

| MODM_FLAGS32 (InterruptFlags) | |

Static Public Member Functions | |

| static void | configure (DataTransferDirection direction, MemoryDataSize memoryDataSize, PeripheralDataSize peripheralDataSize, MemoryIncrementMode memoryIncrement, PeripheralIncrementMode peripheralIncrement, Priority priority=Priority::Medium, CircularMode circularMode=CircularMode::Disabled) |

| static void | start () |

| static void | stop () |

| static DataTransferDirection | getDataTransferDirection () |

| static void | setMemoryAddress (uintptr_t address) |

| static void | setPeripheralAddress (uintptr_t address) |

| static void | setMemoryIncrementMode (bool increment) |

| static void | setPeripheralIncrementMode (bool increment) |

| static void | setDataLength (std::size_t length) |

| static void | setTransferErrorIrqHandler (IrqHandler irqHandler) |

| static void | setHalfTransferCompleteIrqHandler (IrqHandler irqHandler) |

| static void | setTransferCompleteIrqHandler (IrqHandler irqHandler) |

| template<DmaBase::Request dmaRequest> | |

| static void | setPeripheralRequest () |

| static void | interruptHandler () |

| static InterruptFlags_t | getInterruptFlags () |

| static void | clearInterruptFlags (InterruptFlags_t flags=InterruptFlags::All) |

| static void | enableInterruptVector (uint32_t priority=1) |

| static void | disableInterruptVector () |

| static void | enableInterrupt (InterruptEnable_t irq) |

| static void | disableInterrupt (InterruptEnable_t irq) |

Static Protected Attributes | |

| static constexpr uint32_t | configmask |

| static constexpr uint32_t | memoryMask |

| static constexpr uint32_t | peripheralMask |

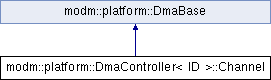

Class representing a DMA channel/stream

|

inheritedstrong |

|

inheritedstrong |

|

inheritedstrong |

In direct mode (if the FIFO is not used) MSIZE is forced by hardware to the same value as PSIZE

|

inheritedstrong |

| Enum Values | Documentation |

|---|---|

| Increment | incremented according to MemoryDataSize |

|

inheritedstrong |

|

inheritedstrong |

Peripheral signals that can be used in DMA channels

|

inlinestatic |

|

inlinestatic |

Configure the DMA channel

Stops the DMA channel and writes the new values to its control register.

| [in] | direction | Direction of the DMA channel |

| [in] | memoryDataSize | Size of data in memory (byte, halfword, word) |

| [in] | peripheralDataSize | Size of data in peripheral (byte, halfword, word) |

| [in] | memoryIncrement | Defines whether the memory address is incremented after a transfer completed |

| [in] | peripheralIncrement | Defines whether the peripheral address is incremented after a transfer completed |

| [in] | priority | Priority of the DMA channel |

| [in] | circularMode | Transfer data in circular mode? |

|

inlinestatic |

Disable the specified interrupt of the channel

|

inlinestatic |

Disable the IRQ vector of the channel

|

inlinestatic |

Enable the specified interrupt of the channel

|

inlinestatic |

Enable the IRQ vector of the channel

| [in] | priority | Priority of the IRQ |

|

inlinestatic |

Get the direction of the data transfer

|

inlinestatic |

Read channel status flags when channel interrupts are disabled. This function is useful to query the transfer state when the use of the channel interrupt is not required for the application.

|

inlinestatic |

IRQ handler of the DMA channel

Reads the IRQ status and checks for error or transfer complete. In case of error the DMA channel will be disabled.

|

inlinestatic |

Set the length of data to be transfered

|

inlinestatic |

Set the IRQ handler for half transfer complete

Called by the channels IRQ handler when the transfer is half complete.

|

inlinestatic |

Set the memory address of the DMA channel

| [in] | address | Source address |

|

inlinestatic |

Enable/disable memory increment

When enabled, the memory address is incremented by the size of the data (e.g. 1 for byte transfers, 4 for word transfers) after the transfer completed.

| [in] | increment | Enable/disable |

|

inlinestatic |

Set the peripheral address of the DMA channel

| [in] | address | Destination address |

|

inlinestatic |

Enable/disable peripheral increment

When enabled, the peripheral address is incremented by the size of the data (e.g. 1 for byte transfers, 4 for word transfers) after the transfer completed.

| [in] | increment | Enable/disable |

|

inlinestatic |

Set the peripheral that operates the channel

|

inlinestatic |

Set the IRQ handler for transfer complete

Called by the channels IRQ handler when the transfer is complete.

|

inlinestatic |

Set the IRQ handler for transfer errors

The handler will be called from the channels IRQ handler function when the IRQ status indicates an error occured.

|

inlinestatic |

Start the transfer of the DMA channel and clear all interrupt flags.

|

inlinestatic |

Stop a DMA channel transfer

|

inheritedstaticprotectedconstexpr |

|

inheritedstaticprotectedconstexpr |

|

inheritedstaticprotectedconstexpr |