|

| enum | Channel {

Stream0 = 0,

Stream1,

Stream2,

Stream3,

Stream4,

Stream5,

Stream6,

Stream7,

Channel0 = Stream0,

Channel1 = Stream1,

Channel2 = Stream2,

Channel3 = Stream3,

Channel4 = Stream4,

Channel5 = Stream5,

Channel6 = Stream6,

Channel7 = Stream7

} |

| |

| enum | CircularMode : uint32_t { Disabled = 0,

CircularMode::Enabled = DMA_SxCR_CIRC

} |

| |

| enum | DataTransferDirection : uint32_t { DataTransferDirection::PeripheralToMemory = 0,

DataTransferDirection::MemoryToPeripheral = DMA_SxCR_DIR_0,

DataTransferDirection::MemoryToMemory = DMA_SxCR_DIR_1

} |

| |

| enum | InterruptEnable : uint32_t { DirectModeError = DMA_SxCR_DMEIE,

TransferError = DMA_SxCR_TEIE,

HalfTransfer = DMA_SxCR_HTIE,

TransferComplete = DMA_SxCR_TCIE

} |

| |

| enum | InterruptFlags : uint8_t {

FifoError = 0b00'0001,

DirectModeError = 0b00'0100,

Error = 0b00'1000,

HalfTransferComplete = 0b01'0000,

TransferComplete = 0b10'0000,

All = 0b11'1101,

Global = All

} |

| |

| enum | MemoryDataSize : uint32_t {

Byte = 0,

Bit8 = Byte,

HalfWord = DMA_SxCR_MSIZE_0,

Bit16 = HalfWord,

Word = DMA_SxCR_MSIZE_1,

Bit32 = Word

} |

| |

| enum | MemoryIncrementMode : uint32_t { Fixed = 0,

MemoryIncrementMode::Increment = DMA_SxCR_MINC

} |

| |

| enum | PeripheralDataSize : uint32_t {

Byte = 0,

Bit8 = Byte,

HalfWord = DMA_SxCR_PSIZE_0,

Bit16 = HalfWord,

Word = DMA_SxCR_PSIZE_1,

Bit32 = Word

} |

| |

| enum | PeripheralIncrementMode : uint32_t { Fixed = 0,

PeripheralIncrementMode::Increment = DMA_SxCR_PINC

} |

| |

| enum | Priority : uint32_t { Low = 0,

Medium = DMA_SxCR_PL_0,

High = DMA_SxCR_PL_1,

VeryHigh = DMA_SxCR_PL_1 | DMA_SxCR_PL_0

} |

| |

| enum | Request : uint32_t {

Channel0 = (0 << DMA_SxCR_CHSEL_Pos),

Channel1 = (1 << DMA_SxCR_CHSEL_Pos),

Channel2 = (2 << DMA_SxCR_CHSEL_Pos),

Channel3 = (3 << DMA_SxCR_CHSEL_Pos),

Channel4 = (4 << DMA_SxCR_CHSEL_Pos),

Channel5 = (5 << DMA_SxCR_CHSEL_Pos),

Channel6 = (6 << DMA_SxCR_CHSEL_Pos),

Channel7 = (7 << DMA_SxCR_CHSEL_Pos)

} |

| |

| enum | Signal : uint8_t {

NoSignal,

Ch1,

Ch2,

Ch3,

Ch4,

Com,

Dac1,

Dac2,

Ext_rx,

Ext_tx,

Rx,

Trig,

Tx,

Up

} |

| |

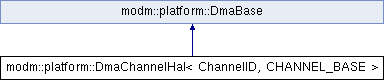

template<DmaBase::Channel ChannelID, uint32_t CHANNEL_BASE>

class modm::platform::DmaChannelHal< ChannelID, CHANNEL_BASE >

Hardware abstraction layer of a DMA channel

- Template Parameters

-

| ChannelID | the ID of the channel |

| CHANNEL_BASE | base address of the channel registers |

- Author

- Mike Wolfram

template<DmaBase::Channel ChannelID, uint32_t CHANNEL_BASE>

| static void modm::platform::DmaChannelHal< ChannelID, CHANNEL_BASE >::setMemoryIncrementMode |

( |

bool |

increment | ) |

|

|

inlinestatic |

Enable/disable memory increment

When enabled, the memory address is incremented by the size of the data (e.g. 1 for byte transfers, 4 for word transfers) after the transfer completed.

- Parameters

-

| [in] | increment | Enable/disable |

template<DmaBase::Channel ChannelID, uint32_t CHANNEL_BASE>

| static void modm::platform::DmaChannelHal< ChannelID, CHANNEL_BASE >::setPeripheralIncrementMode |

( |

bool |

increment | ) |

|

|

inlinestatic |

Enable/disable peripheral increment

When enabled, the peripheral address is incremented by the size of the data (e.g. 1 for byte transfers, 4 for word transfers) after the transfer completed.

- Parameters

-

| [in] | increment | Enable/disable |