|

modm API documentation

|

|

modm API documentation

|

#include <modm/driver/radio/nrf24/nrf24_phy.hpp>

Public Typedefs | |

| typedef FlagsGroup< Feature_t, DynPd_t, FifoStatus_t, Rpd_t, ObserveTx_t, Status_t, RfSetup_t, SetupRetr_t, SetupAw_t, EnRxAddr_t, EnAA_t, Config_t, InterruptFlag_t > | Flags_t |

Public Types | |

| enum | Command : uint8_t { Command::R_REGISTER = 0b00000000, Command::W_REGISTER = 0b00100000, Command::R_RX_PAYLOAD = 0b01100001, Command::W_TX_PAYLOAD = 0b10100000, Command::FLUSH_TX = 0b11100001, Command::FLUSH_RX = 0b11100010, Command::REUSE_TX_PL = 0b11100011, Command::R_RX_PL_WID = 0b01100000, Command::W_ACK_PAYLOAD = 0b10101000, Command::W_TX_PAYLOAD_NOACK = 0b10110000, Command::NOP = 0b11111111 } |

| enum | Config : uint8_t { PRIM_RX = Bit0, PWR_UP = Bit1, CRC0 = Bit2, EN_CRC = Bit3, MASK_MAX_RT = Bit4, MASK_TX_DS = Bit5, MASK_RX_DR = Bit6 } |

| enum | DynPd : uint8_t { DPL_P0 = Bit0, DPL_P1 = Bit1, DPL_P2 = Bit2, DPL_P3 = Bit3, DPL_P4 = Bit4, DPL_P5 = Bit5 } |

| enum | EnAA : uint8_t { ENAA_P0 = Bit0, ENAA_P1 = Bit1, ENAA_P2 = Bit2, ENAA_P3 = Bit3, ENAA_P4 = Bit4, ENAA_P5 = Bit5 } |

| enum | EnRxAddr : uint8_t { ERX_P0 = Bit0, ERX_P1 = Bit1, ERX_P2 = Bit2, ERX_P3 = Bit3, ERX_P4 = Bit4, ERX_P5 = Bit5 } |

| enum | Feature : uint8_t { EN_DYN_ACK = Bit0, EN_ACK_PAY = Bit1, EN_DPL = Bit2 } |

| enum | FifoStatus : uint8_t { RX_EMPTY = Bit0, RX_FULL = Bit1, TX_EMPTY = Bit4, TX_FULL = Bit5, TX_REUSE = Bit6 } |

| enum | InterruptFlag : uint8_t { MAX_RT = Bit4, TX_DS = Bit5, RX_DR = Bit6, ALL = Bit4 | Bit5 | Bit6 } |

| enum | NrfRegister : uint8_t { NrfRegister::CONFIG = 0x00, NrfRegister::EN_AA = 0x01, NrfRegister::EN_RX_ADDR = 0x02, NrfRegister::SETUP_AW = 0x03, NrfRegister::SETUP_RETR = 0x04, NrfRegister::RF_CH = 0x05, NrfRegister::RF_SETUP = 0x06, NrfRegister::STATUS = 0x07, NrfRegister::OBSERVE_TX = 0x08, NrfRegister::RPD = 0x09, NrfRegister::RX_ADDR_P0 = 0x0a, NrfRegister::RX_ADDR_P1 = 0x0b, NrfRegister::RX_ADDR_P2 = 0x0c, NrfRegister::RX_ADDR_P3 = 0x0d, NrfRegister::RX_ADDR_P4 = 0x0e, NrfRegister::RX_ADDR_P5 = 0x0f, NrfRegister::TX_ADDR = 0x10, NrfRegister::RX_PW_P0 = 0x11, NrfRegister::RX_PW_P1 = 0x12, NrfRegister::RX_PW_P2 = 0x13, NrfRegister::RX_PW_P3 = 0x14, NrfRegister::RX_PW_P4 = 0x15, NrfRegister::RX_PW_P5 = 0x16, NrfRegister::FIFO_STATUS = 0x17, NrfRegister::DYNPD = 0x1c, NrfRegister::FEATURE = 0x1d } |

| enum | ObserveTx : uint8_t { ARC_CNT = Bit0 | Bit1 | Bit2 | Bit3, PLOS_CNT = Bit4 | Bit5 | Bit6 | Bit7 } |

| enum | Pipe : uint8_t { PIPE_0 = 0b000, PIPE_1 = 0b001, PIPE_2 = 0b010, PIPE_3 = 0b011, PIPE_4 = 0b100, PIPE_5 = 0b101 } |

| enum | RfCh : uint8_t { RF_CH = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 } |

| enum | RfSetup : uint8_t { RF_PWR = Bit1 | Bit2, RF_DR_HIGH = Bit3, PLL_LOCK = Bit4, RF_DR_LOW = Bit5, CONT_WAVE = Bit7 } |

| enum | Rpd : uint8_t { RPD = Bit0 } |

| enum | RxPwP0 : uint8_t { RX_PW_P0 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | RxPwP1 : uint8_t { RX_PW_P1 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | RxPwP2 : uint8_t { RX_PW_P2 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | RxPwP3 : uint8_t { RX_PW_P3 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | RxPwP4 : uint8_t { RX_PW_P4 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | RxPwP5 : uint8_t { RX_PW_P5 = Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 } |

| enum | SetupAw : uint8_t { AW = Bit0 | Bit1 } |

| enum | SetupRetr : uint8_t { ARC = Bit0 | Bit1 | Bit2 | Bit3, ARD = Bit4 | Bit5 | Bit6 | Bit7 } |

| enum | Status : uint8_t { TX_FULL = Bit0, RX_P_NO = Bit1 | Bit2 | Bit3, MAX_RT = Bit4, TX_DS = Bit5, RX_DR = Bit6 } |

Public Member Functions | |

| MODM_FLAGS8 (Command) | |

| MODM_FLAGS8 (Pipe) | |

| MODM_FLAGS8 (NrfRegister) | |

| MODM_FLAGS8 (Config) | |

| MODM_FLAGS8 (EnAA) | |

| MODM_FLAGS8 (EnRxAddr) | |

| MODM_FLAGS8 (SetupAw) | |

| MODM_FLAGS8 (SetupRetr) | |

| MODM_FLAGS8 (RfCh) | |

| MODM_FLAGS8 (RfSetup) | |

| MODM_FLAGS8 (Status) | |

| MODM_FLAGS8 (ObserveTx) | |

| MODM_FLAGS8 (Rpd) | |

| MODM_FLAGS8 (RxPwP0) | |

| MODM_FLAGS8 (RxPwP1) | |

| MODM_FLAGS8 (RxPwP2) | |

| MODM_FLAGS8 (RxPwP3) | |

| MODM_FLAGS8 (RxPwP4) | |

| MODM_FLAGS8 (RxPwP5) | |

| MODM_FLAGS8 (FifoStatus) | |

| MODM_FLAGS8 (DynPd) | |

| MODM_FLAGS8 (Feature) | |

| MODM_FLAGS8 (InterruptFlag) | |

Static Public Member Functions | |

| static void | initialize (uint8_t payload_length=max_payload_length) |

| static constexpr uint16_t | getMaxPayload () |

| Get the maximum payload size the hardware can transmit in one packet. | |

| static uint8_t | readRegister (NrfRegister_t reg) |

| Read simple 8 bit register. | |

| static void | writeRegister (NrfRegister_t, uint8_t data) |

| Write simple 8 bit register. | |

| static void | setBits (NrfRegister_t reg, Flags_t flags) |

| static void | clearBits (NrfRegister_t reg, Flags_t flags) |

| static void | clearInterrupt (InterruptFlag_t flag) |

| static uint8_t | readRxPayload (uint8_t *buffer) |

| static void | writeTxPayload (uint8_t *buffer, uint8_t len) |

| static void | writeTxPayloadNoAck (uint8_t *buffer, uint8_t len) |

| Same as writeTxPayload() but disable auto ACK for this packet. | |

| static void | writeAckPayload (Pipe_t pipe, uint8_t *buffer, uint8_t len) |

| static void | pulseCe () |

| Send a high pulse of 10us length on Ce pin (blocking) | |

| static void | setCe () |

| static void | resetCe () |

| Set Ce pin low. | |

| static void | flushTxFifo () |

| static void | flushRxFifo () |

| static void | reuseTxPayload () |

| static uint8_t | readRxPayloadWidth () |

| static uint8_t | readStatus () |

| static uint8_t | readFifoStatus () |

| static void | setRxAddress (Pipe_t pipe, uint64_t address) |

| static void | setTxAddress (uint64_t address) |

| static uint64_t | getRxAddress (Pipe_t pipe) |

| static uint64_t | getTxAddress () |

| Get Tx address. | |

| static uint16_t | getPayloadLength () |

| static void | dumpRegisters () |

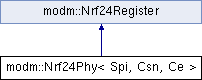

Hardware abstraction layer for nRF24L01+

|

inheritedstrong |

| Enum Values | Documentation |

|---|---|

| R_REGISTER | 1 - 5 data bytes | lower 5 bit = Register address |

| W_REGISTER | 1 - 5 data bytes | lower 5 bit = Register address |

| R_RX_PAYLOAD | 1 - 32 data bytes |

| W_TX_PAYLOAD | 1 - 32 data bytes |

| FLUSH_TX | 0 data bytes |

| FLUSH_RX | 0 data bytes |

| REUSE_TX_PL | 0 data bytes |

| R_RX_PL_WID | 1 data bytes |

| W_ACK_PAYLOAD | 1 - 32 data bytes | lower 3 bit = Pipe # (000 to 101) |

| W_TX_PAYLOAD_NOACK | 1 - 32 data bytes |

| NOP | 0 data bytes |

|

inheritedstrong |

| Enum Values | Documentation |

|---|---|

| CONFIG | |

| EN_AA | Enable 'Auto Acknowledgment'. |

| EN_RX_ADDR | Enabled RX Addresses. |

| SETUP_AW | Setup of Address Widths. |

| SETUP_RETR | Setup of Automatic Retransmission. |

| RF_CH | RF Channel. |

| RF_SETUP | RF Setup Register. |

| STATUS | Status Register. |

| OBSERVE_TX | Transmit observe register. |

| RPD | Received Power Detector. |

| RX_ADDR_P0 | Receive address data pipe 0. |

| RX_ADDR_P1 | Receive address data pipe 1. |

| RX_ADDR_P2 | Receive address data pipe 2. |

| RX_ADDR_P3 | Receive address data pipe 3. |

| RX_ADDR_P4 | Receive address data pipe 4. |

| RX_ADDR_P5 | Receive address data pipe 5. |

| TX_ADDR | Transmit address. |

| RX_PW_P0 | Number of bytes in RX payload in pipe 0. |

| RX_PW_P1 | Number of bytes in RX payload in pipe 1. |

| RX_PW_P2 | Number of bytes in RX payload in pipe 2. |

| RX_PW_P3 | Number of bytes in RX payload in pipe 3. |

| RX_PW_P4 | Number of bytes in RX payload in pipe 4. |

| RX_PW_P5 | Number of bytes in RX payload in pipe 5. |

| FIFO_STATUS | FIFO Status Register. |

| DYNPD | Enable dynamic payload length. |

| FEATURE | Feature Register. |

|

static |

|

inlinestatic |

Flush Rx Fifo

Used in Rx mode. Should not be executed during transmission of acknowledge, that is, acknowledge package will not be completed.

|

inlinestatic |

Flush Tx Fifo Used in Tx mode

|

static |

Get Rx address of pipe

| pipe | Pipe number |

|

inlinestatic |

Initialize nRF24-HAL

Call this function before using this class!

| payload_length | Set fixed payload length in bytes , set 0 for dynamic payload length |

Note: Dynamic payload length is not yet implemented

|

inlinestatic |

Read Fifo status register

|

static |

Read received payload

Used in RX mode. Payload is deleted from FIFO after it is read.

| buffer | buffer where to put payload, should be 32 byte wide |

|

inlinestatic |

Read Rx payload width for top of Rx Fifo Note: Flush RX FIFO if the read value is larger than 32 bytes.

|

static |

Read new status

Note: status will be automatically updated every time a command is issued, so it might not be necessary to call this explicitly.

|

inlinestatic |

Reuse last transmitted payload

Used in PTX mode. TX payload reuse is active until W_TX_PAYLOAD or FLUSH TX is executed. TX payload reuse must not be activated or deactivated during package transmission.

|

static |

Set bits inside a register

Only set individual bits and leave the rest untouched

| reg | Register where to set bits |

| flags | Which bits to set |

|

inlinestatic |

Set Ce pin high If Ce was high before the pin won't be set low before waiting for 10us.

|

static |

Set Rx address for a pipe

Note: pipe 0 and pipe 1 have a 5 byte wide address while pipes 2 to 5 share the upper 4 bytes with pipe 1, so when setting the address of a pipes 2 to 5, only 1 byte (LSB) will be written to SPI.

| pipe | Pipe number, must be in range 0 to 5 |

| address | Address for which packets will be put into pipe, see description concerning differences by pipe |

|

static |

Set Tx address

Used in PTX mode only. Set RX_ADDR_P0 equal to this address to handle automatic acknowledge if this is a PTX device with Enhanced ShockBurst enabled.

| address | Address where to send packets |

|

static |

Write payload to be transmitted together with ACK packet

Used in RX mode. Maximum three ACK packet payloads can be pending. Payloads with same Pipe are handled using first in - first out principle. Write payload: 1– 32 bytes. A write operation always starts at byte 0.

| pipe | Pipe for which the ACK payload is destined, must be in range 0 to 5 |

| buffer | Buffer from where to read the payload |

| len | How many bytes the payload is wide |

|

static |

Write payload to be send

| buffer | Buffer from where to read the payload |

| len | How many bytes the payload is wide |