|

modm API documentation

|

|

modm API documentation

|

#include <modm/platform/dma/dma_hal.hpp>

Public Typedefs | |

| using | IrqHandler = void (*)(void) |

Public Types | |

| enum | Channel { Stream0 = 0, Stream1, Stream2, Stream3, Stream4, Stream5, Stream6, Stream7, Channel0 = Stream0, Channel1 = Stream1, Channel2 = Stream2, Channel3 = Stream3, Channel4 = Stream4, Channel5 = Stream5, Channel6 = Stream6, Channel7 = Stream7 } |

| enum | CircularMode : uint32_t { Disabled = 0, CircularMode::Enabled = DMA_SxCR_CIRC } |

| enum | DataTransferDirection : uint32_t { DataTransferDirection::PeripheralToMemory = 0, DataTransferDirection::MemoryToPeripheral = DMA_SxCR_DIR_0, DataTransferDirection::MemoryToMemory = DMA_SxCR_DIR_1 } |

| enum | InterruptEnable : uint32_t { DirectModeError = DMA_SxCR_DMEIE, TransferError = DMA_SxCR_TEIE, HalfTransfer = DMA_SxCR_HTIE, TransferComplete = DMA_SxCR_TCIE } |

| enum | InterruptFlags : uint8_t { FifoError = 0b00'0001, DirectModeError = 0b00'0100, Error = 0b00'1000, HalfTransferComplete = 0b01'0000, TransferComplete = 0b10'0000, All = 0b11'1101, Global = All } |

| enum | MemoryDataSize : uint32_t { Byte = 0, Bit8 = Byte, HalfWord = DMA_SxCR_MSIZE_0, Bit16 = HalfWord, Word = DMA_SxCR_MSIZE_1, Bit32 = Word } |

| enum | MemoryIncrementMode : uint32_t { Fixed = 0, MemoryIncrementMode::Increment = DMA_SxCR_MINC } |

| enum | PeripheralDataSize : uint32_t { Byte = 0, Bit8 = Byte, HalfWord = DMA_SxCR_PSIZE_0, Bit16 = HalfWord, Word = DMA_SxCR_PSIZE_1, Bit32 = Word } |

| enum | PeripheralIncrementMode : uint32_t { Fixed = 0, PeripheralIncrementMode::Increment = DMA_SxCR_PINC } |

| enum | Priority : uint32_t { Low = 0, Medium = DMA_SxCR_PL_0, High = DMA_SxCR_PL_1, VeryHigh = DMA_SxCR_PL_1 | DMA_SxCR_PL_0 } |

| enum | Request : uint32_t { Channel0 = (0 << DMA_SxCR_CHSEL_Pos), Channel1 = (1 << DMA_SxCR_CHSEL_Pos), Channel2 = (2 << DMA_SxCR_CHSEL_Pos), Channel3 = (3 << DMA_SxCR_CHSEL_Pos), Channel4 = (4 << DMA_SxCR_CHSEL_Pos), Channel5 = (5 << DMA_SxCR_CHSEL_Pos), Channel6 = (6 << DMA_SxCR_CHSEL_Pos), Channel7 = (7 << DMA_SxCR_CHSEL_Pos), Channel8 = (8 << DMA_SxCR_CHSEL_Pos), Channel9 = (9 << DMA_SxCR_CHSEL_Pos), Channel10 = (10 << DMA_SxCR_CHSEL_Pos), Channel11 = (11 << DMA_SxCR_CHSEL_Pos) } |

| enum | Signal : uint8_t { NoSignal, A, B, Ch1, Ch2, Ch3, Ch4, Com, Cs, Dac1, Dac2, Dt, Flt0, Flt1, Flt2, Flt3, In, Out, Rx, Trig, Tx, Up } |

Public Member Functions | |

| MODM_FLAGS32 (InterruptEnable) | |

| MODM_FLAGS32 (InterruptFlags) | |

Static Public Member Functions | |

| static void | clearInterruptFlags (InterruptFlags flags, DmaBase::Channel ChannelID) |

| static uint64_t | getInterruptFlags () |

Static Public Attributes | |

| static constexpr uint32_t | DMA_BASE { getBaseAddress<ID>() } |

| DMA base register address. | |

| static constexpr uint32_t | CHANNEL_BASE { getChannelBaseAddress<ID>() } |

| DMA channel base register address. | |

| static constexpr uint32_t | CHANNEL_2_CHANNEL { 0x18 } |

| Register offset from channel to channel. | |

Static Protected Attributes | |

| static constexpr uint32_t | configmask |

| static constexpr uint32_t | memoryMask |

| static constexpr uint32_t | peripheralMask |

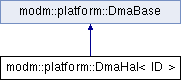

Hardware abstraction of DMA controller

| ID | The number of the DMA controller |

|

inheritedstrong |

|

inheritedstrong |

|

inheritedstrong |

In direct mode (if the FIFO is not used) MSIZE is forced by hardware to the same value as PSIZE

|

inheritedstrong |

| Enum Values | Documentation |

|---|---|

| Increment | incremented according to MemoryDataSize |

|

inheritedstrong |

|

inheritedstrong |

Peripheral signals that can be used in DMA channels

|

inheritedstaticprotectedconstexpr |

|

inheritedstaticprotectedconstexpr |

|

inheritedstaticprotectedconstexpr |